|

|

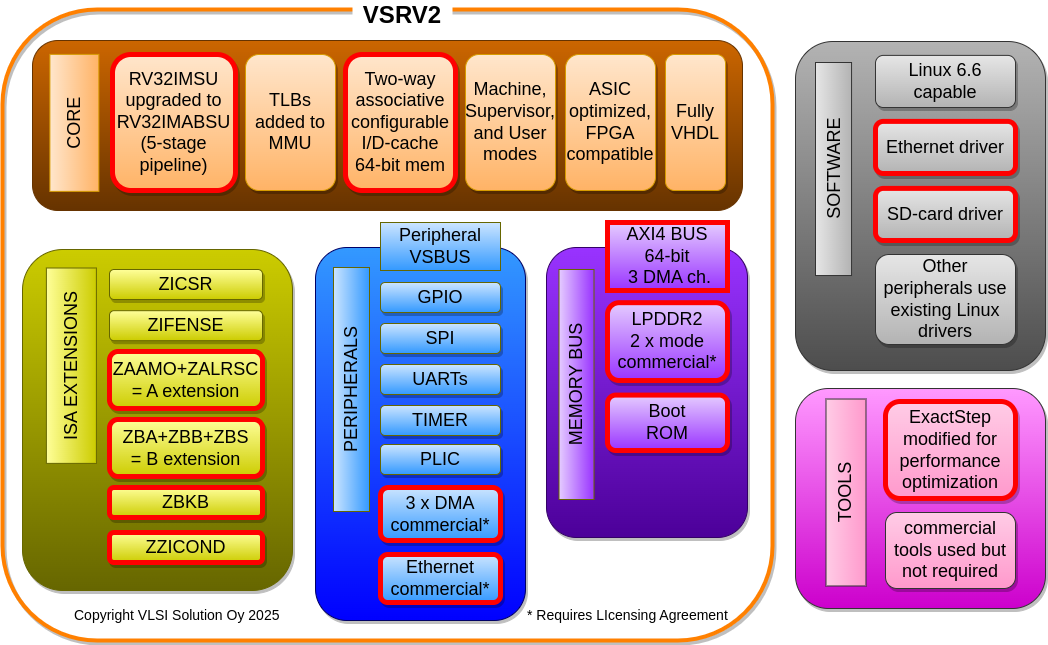

VSRV2 - 32-bit Linux-capable RISC-V CoreFeaturesThe VSRV2 is a second-generation 32-bit RISC-V CPU core that introduces several major enhancements over the VSRV1 baseline architecture (shown with the red color in the above Figure). One of the most significant changes is the increase in the AXI data bus width from 32 bits to 64 bits, which substantially improves memory bandwidth and overall system performance. VSRV2 also incorporates three identical Direct Memory Access channels to handle tasks such as SD-card operations and memory-to-memory copying, effectively reducing processor overhead compared to the VSRV1. Regarding the instruction set architecture, VSRV2 expands on the RV32IM base by adding support for atomic operations, bit manipulation, cryptography extensions, and conditional arithmetic operations. The cache system was also updated to accommodate the wider data path, resulting in a cache line size of 16 words per line in VSRV2 compared to 8 words in VSRV1. Finally, the system hierarchy was restructured to place the debug UART on the same level as the CPU core to simplify debugging and testing procedures. VSRV2 is licensed under permissive Solderpad Hardware License v2. VSRV2 has two internal memory configurations available:

The external memory interface uses the AXI4 bus. We have used an in-house LPDDR2 interface which is not included in the deliveries. FPGA users can use any LPDDR interface supported by the FPGA. The VSRV2 example FPGA setup uses UART, SPI and timer peripherals. Images/setups for Arria 10 device (10AX022C4U19E3SG) and Gidel board (Stratix II device EP2S130F1020C5) are available in the "fpga" directory of the repository.

* You can check the signature in Linux OS with command: sha256sum <filename>.

|