|

|

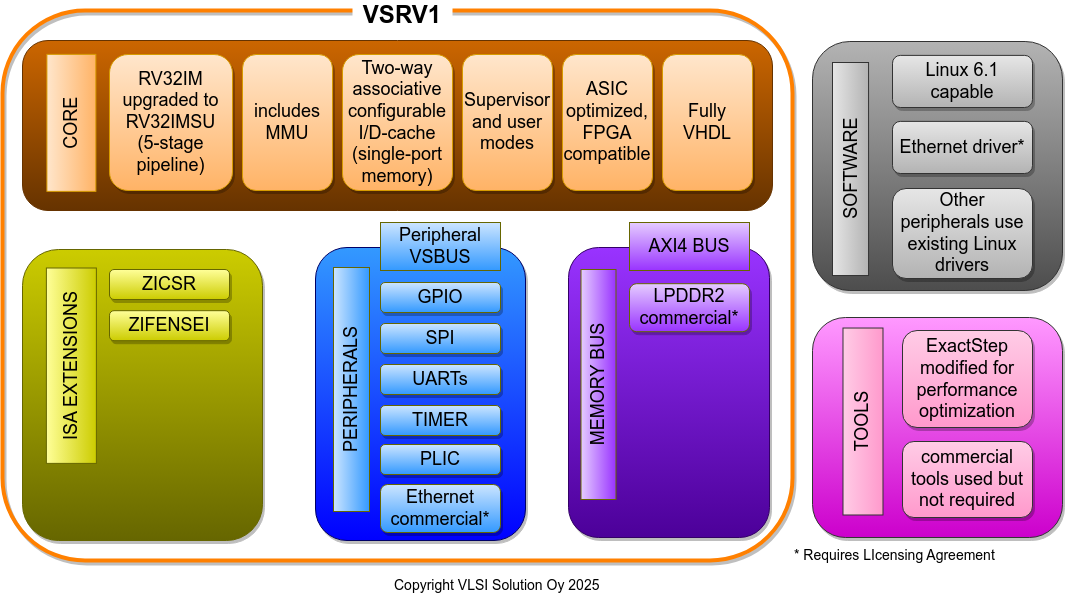

VSRV1 - 32-bit Linux-capable RISC-V CoreFeaturesVSRV1 is a 32-bit RISCV ISA CPU core which supports integer (I), multiplication and division (M), CSR instructions (Z), and supervisory (S) extensions (RV32IMS zicsr zifencei). It has also a rudimentary MMU unit. The "summary of the features" drawing gives a graphical overview of the main features. VSRV1 is licensed under permissive Solderpad Hardware License v2. VSRV1 has two internal memory configurations available:

The external memory interface uses the AXI4 bus. We have used an in-house LPDDR2 interface which is not included in the deliveries. FPGA users can use any LPDDR interface supported by the FPGA. The VSRV1 example FPGA setup uses UART, SPI and timer peripherals. Images/setups for Arria 10 device (10AX022C4U19E3SG) and Gidel board (Stratix II device EP2S130F1020C5) are available in the "fpga" directory of the repository.

* You can check the signature in Linux OS with command: sha256sum <filename>.

|