## VS1033 - MP3/AAC/WMA/MIDI AUDIO CODEC

## Features

Decodes MPEG 1 & 2 audio layer III (CBR +VBR +ABR); layers I & II optional:

MPEG4/2 AAC-LC-2.0.0.0 (+PNS); WMA 4.0/4.1/7/8/9 all profiles (5-384 kbps); WAV (PCM + IMA ADPCM);

- General MIDI / SP-MIDI format 0 files

Encodes IMA ADPCM from microphone or line input

- Streaming support for MP3 and WAV

- EarSpeaker Spatial Processing

- Bass and treble controls

- Operates with a single clock 12..13 MHz

- Can also be used with 24..26 MHz clocks

- Internal PLL clock multiplier

- Low-power operation

- High-quality on-chip stereo DAC with no phase error between channels

- Stereo earphone driver capable of driving a 30  $\Omega$  load

- Quiet power-on and power-off

- I2S interface for external DAC

- Separate operating voltages for analog, digital and I/O

- 5.5 KiB On-chip RAM for user code / data

- Serial control and data interfaces

- Can be used as a slave co-processor

- SPI flash boot for special applications

- UART for debugging purposes

- New functions may be added with software and 8 GPIO pins

- Lead-free RoHS-compliant package (Green)

#### 12S audic VS1033 mic audio Stereo Ear-≻ L MUX Mono ADC Stereo DAC MIC AMP > R line audio output GPIO GPIO X ROM DREC SO Serial Data/ Control Interfac SI X RAM SCLK VSDSP<sup>4</sup> XCS XDCS Y ROM RX UART τх Y RAM Clock nultiplier Instruction RAM Instruction BOM

## Description

VS1033 is a single-chip MP3/AAC/WMA/MIDI audio decoder and ADPCM encoder. It contains a high-performance, proprietary low-power DSP processor core VS\_DSP<sup>4</sup>, working data memory, 5 KiB instruction RAM and 0.5 KiB data RAM for user applications, serial control and input data interfaces, upto 8 general purpose I/O pins, an UART, as well as a highquality variable-sample-rate mono ADC and stereo DAC, followed by an earphone amplifier and a common voltage buffer.

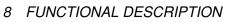

VS1033 receives its input bitstream through a serial input bus, which it listens to as a system slave. The input stream is decoded and passed through a digital volume control to an 18-bit oversampling, multi-bit, sigmadelta DAC. The decoding is controlled via a serial control bus. In addition to the basic decoding, it is possible to add application specific features, like DSP effects, to the user RAM memory.

EarSpeaker spatial processing provides more natural sound in headphone listening conditions. It widens the stereo image and positions the sound sources outside the listener's head.

## Contents

| VS | S1033                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                    |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Та | able of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                    |

| Li | st of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                                                                                                                                                                                                                                                    |

| 1  | Licenses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                                                                                                                                                                                                                                    |

| 2  | Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                                                                                                                                                                                                    |

| 3  | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                                                                                                                                                                                                                                    |

| 4  | Characteristics & Specifications4.1Absolute Maximum Ratings4.2Recommended Operating Conditions4.3Analog Characteristics4.4Power Consumption4.5Digital Characteristics4.6Switching Characteristics - Boot Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 8<br>. 9<br>. 10<br>. 10                                                                                                                                                                                                                           |

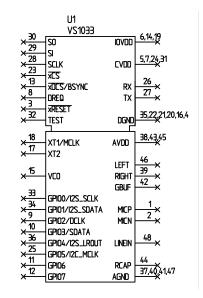

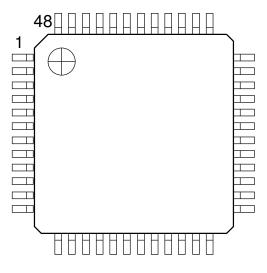

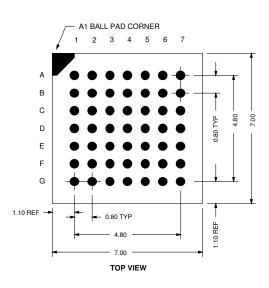

| 5  | Packages and Pin Descriptions5.1Packages5.1.1LQFP-485.1.2BGA-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 11                                                                                                                                                                                                                                                 |

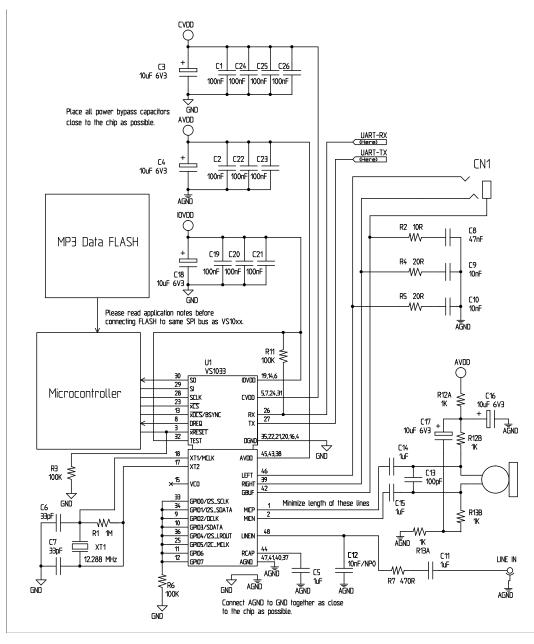

| 6  | Connection Diagram, LQFP-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14                                                                                                                                                                                                                                                   |

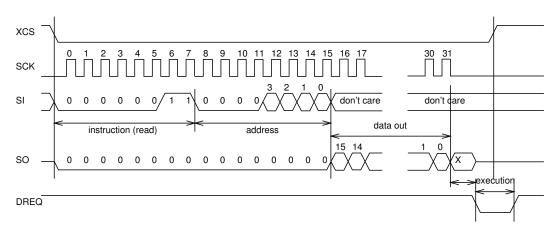

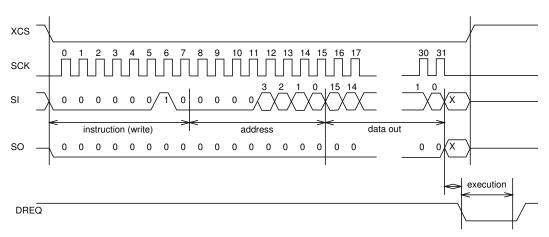

| 7  | SPI Buses         7.1       General         7.2       SPI Bus Pin Descriptions         7.2.1       VS1002 Native Modes (New Mode)         7.2.2       VS1001 Compatibility Mode         7.3       Data Request Pin DREQ         7.4       Serial Protocol for Serial Data Interface (SDI)         7.4.1       General         7.4.2       SDI in VS1002 Native Modes (New Mode)         7.4.3       SDI in VS1002 Native Modes (New Mode)         7.4.4       Passive SDI Mode         7.5       Serial Protocol for Serial Command Interface (SCI)         7.5.1       General         7.5.2       SCI Read         7.5.3       SCI Write         7.5.4       SCI Multiple Write | 15         15         15         16         16         16         16         17         17         17         17         17         17         17         17         17         17         17         17         17         18         18         19 |

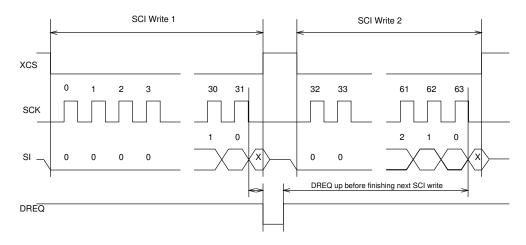

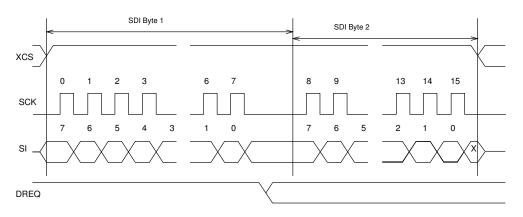

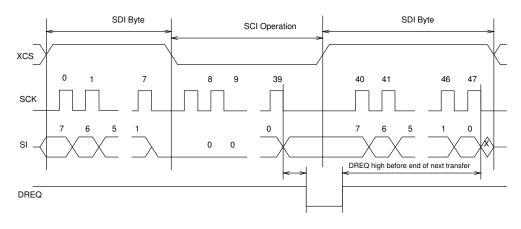

|    | 7.6       SPI Timing Diagram         7.7       SPI Examples with SM_SDINEW and SM_SDISHARED set         7.7.1       Two SCI Writes         7.7.2       Two SDI Bytes         7.7.3       SCI Operation in Middle of Two SDI Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 21<br>. 21<br>. 21                                                                                                                                                                                                                                 |

| 8  | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23                                                                                                                                                                                                                                                   |

#### 8 Functional Description

|   | 8.1                                                         | Main Feat                                                                                                                                                                                                                                         | ures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5          |

|---|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   | 8.2                                                         | Supported                                                                                                                                                                                                                                         | 1 Audio Codecs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | j          |

|   |                                                             | 8.2.1                                                                                                                                                                                                                                             | Supported MP3 (MPEG layer III) Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5          |

|   |                                                             | 8.2.2                                                                                                                                                                                                                                             | Supported MP1 (MPEG layer I) Formats 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ļ          |

|   |                                                             | 8.2.3                                                                                                                                                                                                                                             | Supported MP2 (MPEG layer II) Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ļ          |

|   |                                                             | 8.2.4                                                                                                                                                                                                                                             | Supported AAC (ISO/IEC 13818-7) Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ;          |

|   |                                                             | 8.2.5                                                                                                                                                                                                                                             | Supported WMA Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|   |                                                             | 8.2.6                                                                                                                                                                                                                                             | Supported RIFF WAV Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   |                                                             | 8.2.7                                                                                                                                                                                                                                             | Supported MIDI Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

|   | 8.3                                                         | -                                                                                                                                                                                                                                                 | of VS1033                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|   | 8.4                                                         |                                                                                                                                                                                                                                                   | er Spatial Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

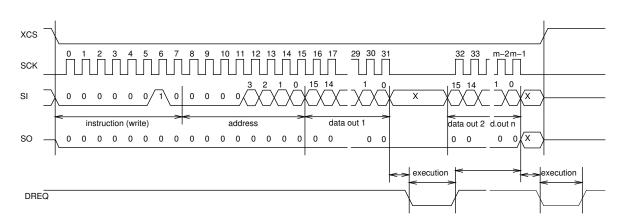

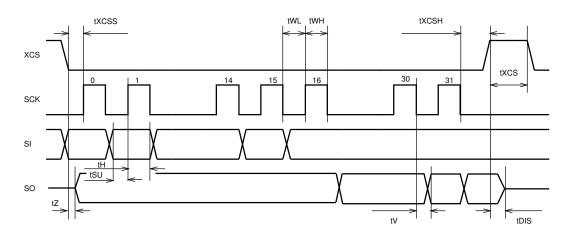

|   | 8.5                                                         |                                                                                                                                                                                                                                                   | a Interface (SDI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|   | 8.6                                                         |                                                                                                                                                                                                                                                   | ntrol Interface (SCI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|   | 8.7                                                         |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   | 0.7                                                         | 8.7.1                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   |                                                             |                                                                                                                                                                                                                                                   | _ ( )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|   |                                                             | 8.7.2                                                                                                                                                                                                                                             | SCI_STATUS (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   |                                                             | 8.7.3                                                                                                                                                                                                                                             | SCI_BASS (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|   |                                                             | 8.7.4                                                                                                                                                                                                                                             | SCI_CLOCKF (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   |                                                             | 8.7.5                                                                                                                                                                                                                                             | SCI_DECODE_TIME (RW) 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|   |                                                             | 8.7.6                                                                                                                                                                                                                                             | SCI_AUDATA (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   |                                                             | 8.7.7                                                                                                                                                                                                                                             | SCI_WRAM (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|   |                                                             | 8.7.8                                                                                                                                                                                                                                             | SCI_WRAMADDR (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | )          |

|   |                                                             | 8.7.9                                                                                                                                                                                                                                             | SCI_HDAT0 and SCI_HDAT1 (R) 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )          |

|   |                                                             | 8.7.10                                                                                                                                                                                                                                            | SCI_AIADDR (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   |                                                             | 8.7.11                                                                                                                                                                                                                                            | SCI_VOL (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,          |

|   |                                                             | 0.7.11                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •          |

|   |                                                             | 8.7.12                                                                                                                                                                                                                                            | SCI_AICTRL[x] (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| • | 0                                                           | 8.7.12                                                                                                                                                                                                                                            | SCI_AICTRL[x] (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2          |

| 9 | Opera                                                       | 8.7.12<br>ation                                                                                                                                                                                                                                   | SCI_AICTRL[x] (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2          |

| 9 | 9.1                                                         | 8.7.12<br>ation<br>Clocking                                                                                                                                                                                                                       | SCI_AICTRL[x] (RW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )<br>-<br> |

| 9 | 9.1<br>9.2                                                  | 8.7.12<br><b>ation</b><br>Clocking<br>Hardware                                                                                                                                                                                                    | SCI_AICTRL[x] (RW)       42         43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| 9 | 9.1<br>9.2<br>9.3                                           | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software                                                                                                                                                                                               | SCI_AICTRL[x] (RW)       42         43         43         Reset       43         Reset       43         Reset       43         44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| 9 | 9.1<br>9.2                                                  | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software I<br>ADPCM F                                                                                                                                                                                  | SCI_AICTRL[x] (RW)       42         43         43         Reset       43         Reset       43         Reset       43         Reset       43         43       43         44       44         8ecording       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| 9 | 9.1<br>9.2<br>9.3                                           | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software I<br>ADPCM F<br>9.4.1                                                                                                                                                                         | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Recording       44         Activating ADPCM Mode       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| 9 | 9.1<br>9.2<br>9.3                                           | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software I<br>ADPCM F<br>9.4.1<br>9.4.2                                                                                                                                                                | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Recording       44         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

| 9 | 9.1<br>9.2<br>9.3                                           | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3                                                                                                                                                         | SCI_AICTRL[x] (RW)       42         43         Reset       44         Recording       44         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

| 9 | 9.1<br>9.2<br>9.3                                           | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.3<br>9.4.4                                                                                                                                       | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       44         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| 9 | 9.1<br>9.2<br>9.3                                           | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3                                                                                                                                                         | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Recording       44         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| 9 | 9.1<br>9.2<br>9.3                                           | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.3<br>9.4.4                                                                                                                                       | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       44         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| 9 | 9.1<br>9.2<br>9.3                                           | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software I<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.3<br>9.4.4<br>9.4.5                                                                                                                            | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Recording       44         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

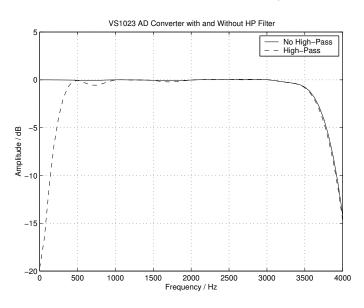

| 9 | 9.1<br>9.2<br>9.3                                           | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.6<br>9.4.7                                                                                                            | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Reset       43         Reset       43         Reset       43         Recording       44         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         AD Startup Time       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| 9 | 9.1<br>9.2<br>9.3<br>9.4                                    | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.5<br>9.4.6<br>9.4.7<br>SPI Boot                                                                                       | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       44         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         AD Startup Time       48         Example Code       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 9 | 9.1<br>9.2<br>9.3<br>9.4                                    | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software I<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.5<br>9.4.6<br>9.4.7<br>SPI Boot<br>Real-Time                                                                                 | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Recording       44         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         AD Startup Time       48         Example Code       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

| 9 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6                      | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.5<br>9.4.6<br>9.4.7<br>SPI Boot<br>Real-Time<br>Play/Deco                                                             | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Reset       43         Reset       43         Recording       44         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         AD Startup Time       48         Example Code       48         MIDI       50         MIDI       50                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

| 9 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7               | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.5<br>9.4.6<br>9.4.7<br>SPI Boot<br>Real-Time<br>Play/Deco<br>Feeding F                                                | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Reset       43         Recording       44         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         AD Startup Time       48         Example Code       50         MIDI       50         OCM data       51                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| 9 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8        | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.5<br>9.4.6<br>9.4.7<br>SPI Boot<br>Real-Time<br>Play/Deco<br>Feeding F                                                | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Reset       43         Recording       44         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         AD Startup Time       48         Example Code       50         MIDI       50         OCM data       51                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| 9 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8        | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software I<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.6<br>9.4.7<br>SPI Boot<br>Real-Time<br>Play/Deco<br>Feeding P<br>Extra Para                                                  | SCI_AICTRL[x] (RW)       42         Reset       43         Reset       43         Reset       43         Recording       45         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         AD Startup Time       48         Example Code       50         MIDI       50         Odd       51         Adata       51         Anders       51         Sample Rate       50         Startup Time       50         Sample Code       50         Startup Time       50 |            |

| 9 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8        | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software I<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.6<br>9.4.7<br>SPI Boot<br>Real-Time<br>Play/Deco<br>Feeding P<br>Extra Para<br>9.9.1<br>9.9.2                                | SCI_AICTRL[x] (RW)       42         Reset       43         Reset       43         Reset       43         Recording       44         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         Example Code       50         MIDI       50         Ode       50         YMA       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| 9 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8        | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software I<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.6<br>9.4.7<br>SPI Boot<br>Real-Time<br>Play/Decc<br>Feeding F<br>Extra Para<br>9.9.1<br>9.9.2<br>9.9.3                       | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Reset       44         Recording       44         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         AD Startup Time       48         Example Code       50         MIDI       50         Ode       50         WMA       54         AAC       54                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| 9 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9 | 8.7.12<br>ation<br>Clocking<br>Hardware<br>Software I<br>ADPCM F<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.6<br>9.4.7<br>SPI Boot<br>Real-Time<br>Play/Deco<br>Feeding F<br>Extra Para<br>9.9.1<br>9.9.2<br>9.9.3<br>9.9.4              | SCI_AICTRL[x] (RW)       42         43         Reset       43         Reset       43         Reset       43         Recording       44         Activating ADPCM Mode       45         Reading IMA ADPCM Data       46         Adding a RIFF Header       46         Playing ADPCM Data       47         Sample Rate Considerations       48         AD Startup Time       48         Example Code       50         MIDI       50         Odd       51         Ameters       52         Common Parameters       53         WMA       54         AAC       54                                                                                                                                                                                                                                                                                                                                                                                               |            |